DDL(可调延迟线)测试概述

在DDR4多PHY PHY模块中,嵌入了多种可调延迟线(DDL),其基本逻辑功能是缓冲器。测试这些DDL以确保其正常工作和产生正确的延迟值是非常重要的。以下是对DDL测试过程的详细解释。

1. DDL的基本功能

- 可调延迟线(DDL):

- DDL是一种可调节的延迟线,允许在信号传输路径中引入特定的延迟,以补偿时序上的偏差。不同类型的DDL(如LCDL、BDL和NDL)被用于不同的应用场景。

- 内部逻辑扫描测试:

- 内部逻辑扫描测试通过将信号从DDL的输入传递到输出,验证DDL能够正确传递逻辑0和1。但是,该测试无法验证每个DDL设置是否产生唯一的延迟值,或者这些延迟值是否组合成特定的延迟特性。

2. DDL的类型与用途

LCDL(Local Calibrated Delay Line):

用途:用于DQ/DQS信号的偏移调整。

特点:可调节的延迟线,允许在数据传输中引入可变的延迟,以便精确对齐数据和时钟信号。

BDL(Buffer Delay Line):

用途:用于DATX8和DATX4X2块中的读写比特去偏移(deskew)。

特点:相较于LCDL,BDL的最大延迟较短,主要用于较小的延迟调整。

NDL(Fixed Delay Line):

用途:用于匹配LCDL的零延迟。

特点:具有固定的延迟值,不可调节,主要用于为LCDL提供基准延迟。

总结:

可调性:LCDL和BDL是可调的,而NDL是固定的。

延迟范围:LCDL提供较大的延迟调节范围,BDL则提供相对较短的延迟。

应用场景:LCDL主要用于数据对齐,BDL用于读写比特的去偏移,NDL用于提供固定延迟。

LCDL与BDL:

- LCDL(本地校准延迟线)用于DQ/DQS偏移,而BDL(短延迟线)用于DATX8和DATX4X2块中的读写比特去偏移。NDL(固定延迟线)用于匹配LCDL的零延迟。

可观察性:

- 某些DDL(例如DATX8和DATX4X2中的写比特去偏移DDL)是可观察的,可以通过发送特定的数据模式并直接编程DDL延迟值来检测输出延迟的变化。然而,不是所有DDL都会影响设备的主要输出,某些DDL只影响内部节点。

3. DDL的测试挑战

- 测量限制:

- DDL的最小延迟步长非常小,超出了大多数自动测试设备(ATE)的测量能力。这意味着只能在较大的步长上进行特性测试,这不是理想的解决方案。

- 直接访问:

- 通过直接访问DDL的延迟值寄存器,尽管可以进行一些初步测试,但这并不能完全解决所有DDL的测试需求。

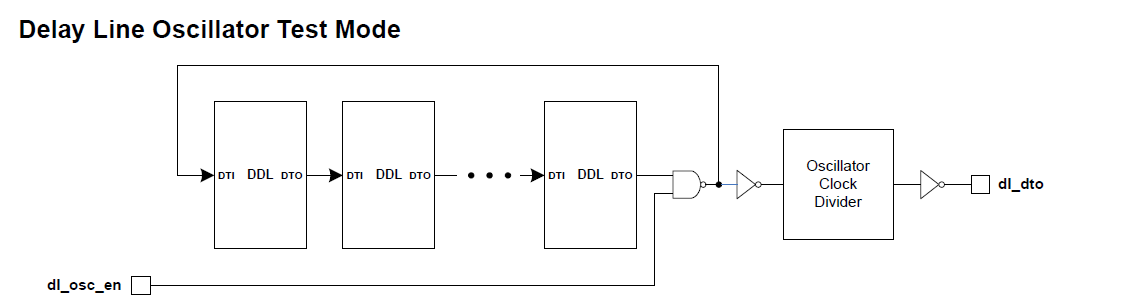

4. DDL环振荡器测试模式

为了更全面地测试DDL,所有PHY块和PUB中都集成了DDL环振荡器测试模式。

- 环振荡器的构建:

- 在环振荡器测试模式中,NDL、BDL和LCDL被连接在一起,形成一个单一的环形振荡器。这是通过将一个延迟线的数字测试输出(DTO)连接到另一个延迟线的数字测试输入(DTI)来实现的。

- 振荡器输出与分频:

- 环振荡器的输出通过一个可编程的分频器进行分频,产生的输出信号作为延迟线测试输出。每个DATX8、PHYDATX4X2、PHYAC和PHYACX48模块都有自己的环,允许并行测试整个接口。

- 自动测量功能:

- PUB中有额外的逻辑,可以自动测量延迟线测试输出的周期。测量的周期可以从寄存器中读取,并以相对于PUB控制器时钟(ctl_clk)周期的代码表示。

5. 测试过程示例

假设我们希望测试一个LCDL的性能:

- 初始化:

- 确保PLL锁定并触发延迟线校准。

- 进入环振荡器模式:

- 启用DDL环振荡器测试模式,将所有相关DDL连接成一个环。

- 编程延迟线:

- 通过设置DDL的延迟值,调整环中每个DDL的延迟。

- 观察输出:

- 通过环的输出观察振荡信号的频率变化,记录输出的周期。

- 分析结果:

- 通过对比输出周期与期望值,评估每个DDL的延迟性能,确保它们在预期范围内工作。

通过这种方法,工程师可以获得DDL的线性度和范围,确保整个DDR4接口的可靠性和性能。

DDL的组成

粗延迟元素(Coarse Delay Elements):

- 这些元素提供较大的延迟步长。它们的数量因不同类型的DDL而异:

- BDL(Buffer Delay Line):包含4个粗延迟元素。

- 下四位([3:0])对应于细粒度延迟位。

- 上两位([5:4])对应于粗粒度延迟位。

- LCDL(Local Calibrated Delay Line):包含32个粗延迟元素。

- 下四位([3:0])同样对应于细粒度延迟位。

- 上五位([8:4])对应于粗粒度延迟位。

- BDL(Buffer Delay Line):包含4个粗延迟元素。

细延迟元素(Fine Delay Element):

- 这是一个可调的细微延迟元素,可以提供更精确的延迟调整。在BDL和LCDL中,细延迟元素的数量是相同的:

- 都包含16个细微步长。

如何设置DDL延迟

- 在设置某个DDL延迟时,可以通过选择一定数量的粗延迟元素和细延迟元素的组合来实现。

- 例如,如果需要某个特定的延迟:

- 可以选择2个粗延迟元素(BDL)或4个粗延迟元素(LCDL),然后可能再加上1到16个细微延迟步长。

举个例子

假设你需要设置一个特定的延迟为200个时钟周期(tCK):

- 在BDL中:

- 选择2个粗延迟元素(每个元素提供50个时钟周期的延迟),总共提供100个时钟周期的延迟。

- 然后可以使用细延迟元素,选择6个细微步长(每个细微步长提供约16.67个时钟周期的延迟),总共提供100个时钟周期的延迟。

- 最终组合为100 + 100 = 200个时钟周期。

- 在LCDL中:

- 选择3个粗延迟元素(每个元素提供50个时钟周期的延迟),总共提供150个时钟周期的延迟。

- 再使用3个细微步长(每个细微步长提供约16.67个时钟周期的延迟),总共提供50个时钟周期的延迟。

- 最终组合为150 + 50 = 200个时钟周期。

总结

这种设计允许在较大范围内快速设置和微调延迟,使得在不同的操作条件下能够实现精确的时序控制。不同类型的DDL通过不同数量的粗细延迟元素组合来提供所需的延迟特性。

可调延迟线(DDL)测试的两种观察方法

主要是通过环形振荡器的输出信号来进行测试。这两种方法在测试的有效性和效率上有所不同。

1. 环形振荡器输出

- 环形振荡器是通过连接多个延迟线构成的一个电路,能产生稳定的时钟信号。

- 这个时钟信号会在经过可编程分频器后送入PUB(物理单元控制器)。

2. 测试观察方法

方法一:自动计算频率

- PUB可以计算出环形振荡器输出的时钟频率,并通过取样功能得出这个频率值。

- 由于控制器时钟(ctl_clk)可能在较慢的速度下运行,能够通过设置适当的时钟分频比来保证测试的准确性和减少测试时间。

- 优点:这种方法允许所有PHY块(包括AC/ACX48和每个DATX8/DATX4X2)并行测试,提高了测试效率。

方法二:数字测试输出

- 将分频后的时钟信号直接输出到数字测试输出(dto[0]),使用户能够直接观察时钟波形。

- 优点:这种方法在设备调试和特性测试时比较有用,因为用户可以直接看到波形。

- 缺点:对于生产测试来说,这种方法不是最优的,因为只能一次查看一个PHY块,效率较低。

举个例子

假设在生产测试过程中,设计团队需要测试多个PHY块的延迟线:

使用方法一

- 将所有PHY块连接到PUB。PUB自动计算每个块的环形振荡器频率,并输出结果。这个过程是并行进行的,可以快速完成多个测试。

使用方法二

- 如果选择直接观察分频后的时钟信号,测试人员需要逐个连接每个PHY块,并观察其时钟波形。这意味着在测试过程中,必须一一检查,耗时较长。

总结

这段描述强调了测试DDL的两种方法的优缺点。在生产测试中,自动计算频率的方法能够提高效率,而直接观察时钟波形则适合调试和特性测试场景。选择合适的方法可以有效地优化测试过程。

本文链接: https://talent-tudou.github.io/2024/10/27/DDR/DLL Testing/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!